|

|

PLL アーキテクチャ 3 Multiple Loop |

| PL03S/04S |

■ MULTIPLE LOOP SERIES について

|

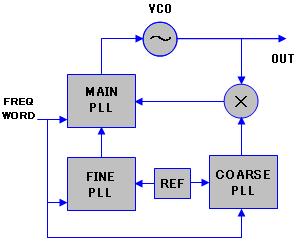

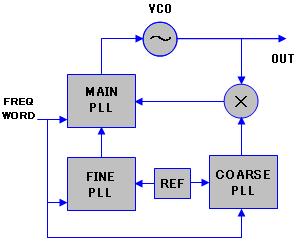

| 図-3. PLL Multiple Loop の基本構成図 |

図-3 は、Multiple Loop PLL の 1つの構成例を示します。

ここでは、MAIN PLL Loop に ミキサ を ともなった COARSE PLL 及び REF入力側には FINE PLL Loop が追加されています。

COARSE PLL Loop は REF の信号を もとにした ステップサイズの大きな周波数シンセサイザで ローノイズ信号であり、この信号との ミックス・ダウン に

よって MAIN PLL Loop の 分周比を 少なくすることができます。

さらに、FINE PLL Loop が 追加されることにより、低位相雑音でありながら 周波数ステップサイズを細かく設定でき、チューニング スピード や スプ

リアス特性の 優れた 周波数シンセサイザ の提供が可能となります。

RFDN では、独自に開発・設計した ローノイズ VCO や VCXO を用いた COARSE PLL や COM Generator を用いることにより、お客様の仕様を満足す

る MULTIPLE LOOP を 提案、設計することが可能です。

* YIG同調発振(YTO) を用いた 高周波 ローノイズ MULTIPLE LOOP 周波数シンセサイザ の開発 経験もあり得意と

しています。

残念ながら、個人事業 としては 費用・設備の問題から、あまり大きな規模の設計を受託できませんが、お手伝いすることは可能です!