|

|

PLL アーキテクチャ 2 Dual Loop |

| PL02S |

■ DUAL LOOP SERIES について

|

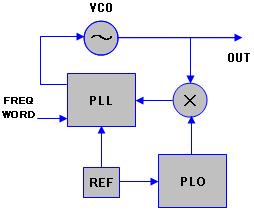

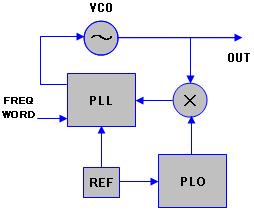

| 図-2. PLL Dual Loop の基本構成図 |

図-2 は、Dual Loop PLL の 基本構成で PLL に もう1つの PLO Loop が ミキサ と ともに追加された形となっています。

通常、この PLO Loop は REF. の周波数を てい倍 した 固定出力の周波数シンセサイザとなっており、この ミックス・ダウン の プロセス に

よって PLL Loop の 分周比を 少なくすることができ、位相雑音 及び チューニング スピード を Single Loop では 達成し得ないレベルに

まで 性能アップ することができます。

RFDN では、独自に開発・設計した ローノイズ VCO や VCXO を用いて、さらに PLO 及び PLL Loop の ループフィルタ の最適設計をすることにより、極く 低位相雑音

の 周波数シンセサイザを ご提供 することが可能です。

* 出力周波数の範囲、必要なステップ・サイズ、位相雑音特性 等の 仕様 を お知らせ下さい!

RFDN の 技術レベル で どの規模の 周波数シンセサイザ で 達成することができるかを検討 致します。