|

PLL ループ・フィルター の設計方法 |

PllNote |

あらまし 周波数シンセサイザー PLL 回路における ループ・フィルターの設計 には様々な要素

が絡み合い、非常に難しい面がある。

ここでは、単に ロック すれば良いのではなく、位相雑音 C/N 値 の 側面から見た 最適な ループ・フィルターをどのように決めるかを 設計例 を用いて説明する。

分周比 N の違いによって どのように ループ・フィルターのカットオフ周波数が変化するのか。 また、Phase Margin 位相余裕の値によって 閉ループ

特性はどのように変化するのか。 それにより 位相雑音 C/N 値は どうなるのかを シミュレーション して考察する。

■ 1. 設計する PLL回路

|

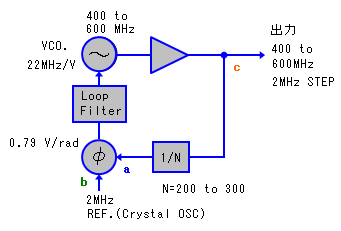

| 図-1. 設計する PLL.回路の構成 |

図-1. には、今回 机上設計する PLL.回路の構成を記す。

ここで、 VCO. は 400MHz から 600MHz の発振帯域を有し その感度は 22 MHz/Volt となっている。

また、Phase Detector 位相比較器のゲイン定数は 0.79 V/rad であり、1/N 分周は N = 200 から 300 の可変分周器が用いられている。

そして、位相比較器への Reference 基準信号は 2 MHz のクリスタル発振器が用いられ、その結果 出力には 400MHz から 600MHz の 2MHz ステップ の周波数シンセサイザ PLL.回路が構成される。

■ 2. ループ・フィルター カットオフ周波数 fc の最適値

ループ・フィルター カットオフ周波数 fc の理想値は 次のように選定される。

十分なオープンゲインを有する PLL で VCO. を ロックすると 図-1. に示す Phase Detector の両入力信号 a, b の位相雑音は等しくなる。

すなわち、VCO. の位相雑音は 基準信号レベルまで 改善できるのだが、今回の 2MHz ステップ シンセの場合 VCO. と Phase Detector の

間に 1/N 分周器が入り、分周器入力 c から見た基準信号の位相雑音は 20 log N だけ悪くなる。

例えば、基準信号 クリスタル OSC. からの 2 MHz の 1 MHz offset.( 離れの) C/N.値が -155dBc/Hz として、600MHz 発振時 N = 300 の場合、

-155dBc/Hz + 20 log (300) ≒ -105dBc/Hz と悪化してしまう。

ここで、1 MHz offset. C/N.値が ≒ -105dBc/Hz であれば、VCO.の 1 MHz offset. C/N.値の方が下がっているはずである。

|

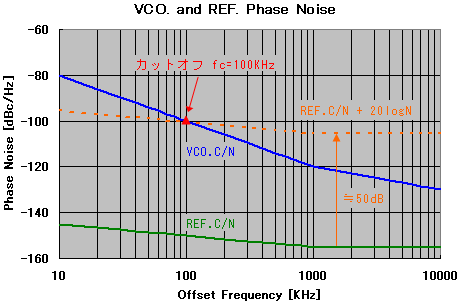

| 図-2. VCO.とREF. C/N.値 fc との関係 |

図-2. は、これを説明するもので 青い線 で記したものは VCO.の位相雑音 C/N.値を示し、緑の線 で記した C/N.値は REF. 2 MHz のクリスタル 発振器を示し、オレンジ点線 は その N 倍 悪化した 位相雑音 C/N.値を表している。

すなわち、Offset.周波数 100KHz を境にして、近ぼう では クリスタル発振器の N 倍 悪化した 位相雑音 が良い特性を示し、遠ぽう では VCO. の 位相雑音 の方が良好な特性となっている。

ということは、Offset.周波数 100KHz を ループ・フィルター カットオフ周波数 fc にできれば もっとも 位相雑音 C/N.値の良い 周波数シンセサイザー PLL.回路を 得ることが可能となる。

■ 3. ループ・フィルター の 設計

ここで、ループ・フィルター の設計は ループ・フィルター設計ツール を用いて計算する。

ループ・フィルター 設計条件の入力画面において、設計例 ボタンをクリックすると 今回の 図-1 に示す条件に加え Phase Margin 位相余裕 45°及び N=300 が入力される。

START ボタンを続けてクリックすると 設計プログラムが 走り、ループ・フィルター 選択の画面となる。

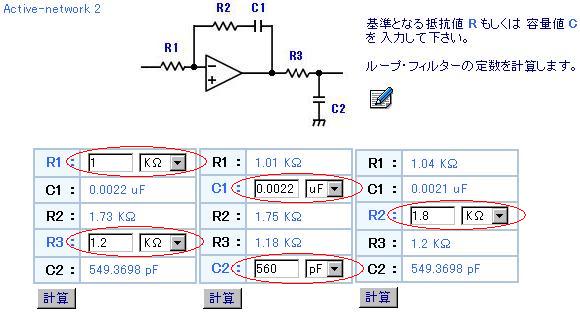

次に、ループ・フィルター は 今回 Active-network 2 を用いることにする。

( 同じ次数のフィルターでも network 1 の方が少ない部品で構成されるが、network 2 は VCO.の直前に R3・C2 のフィルターを配置でき、定数も R3・C2 は個別に設定でき 変更しやすく

なっている )。

図-3 は、ループ・フィルター 設計画面 であり R1 を 1KΩ とすると C2 は 0.0022uF と算出され、実際に用いることのできる定数となっている。 R2 は 1.73KΩ

と算出されたが、これは実際の値がないので 近い値である 1.8KΩ を R2 に入れて計算させると、R1 は 1.04KΩ そして C1 は 0.0021uF となり ほぼ問題ないことが確かめられる。

同様に R3 と C2 も追い込み 実際に用いることのできる定数を得ることができる。

|

| 図-3. Active-network 2 ループ・フィルター 設計画面 |

カットオフ周波数 fc≒ 100KHz で Phase Margin 位相余裕 45°の ループ・フィルター の定数は

R1=1KΩ, C1=0.0022uF, R2=1.8kΩ, R3=1.2KΩ, C2=560pF という値を求めることができた。

なお、この ループ・フィルター設計ツール は、Phase Lock Loop を 3次ループとして 伝達関数を用いて解いているのだが、計算式 等は 別の機会に まとめる ことにする。

■ 4. PLL ループ 応答特性

次に、上で決めた ループ・フィルター の値で、どのような PLL ループ 応答特性となるのかを シミュレーション する。

図-4 は、N = 300 で計算した R1=1KΩ, C1=0.0022uF, R2=1.8kΩ, R3=1.2KΩ, C2=560pF の ループ・フィルターを用いた時の Open loop Gain (開ループ・ゲイン), Closed loop Modulus (閉ループ係数), Noise Reduction ( VCO.位相雑音をループがどの程度に抑圧するか) 及び Phase Margin (位相余裕) を 計算したものである。

オフセット周波数 100KHz で Open loop Gain は 0 dB となり、その時の Phase Margin (位相余裕)は 45°と設計値どおりとなっている。

しかしながら、この ループ・フィルターで 出力周波数を 600MHz から 400MHz に設定する場合、 N = 300 から N = 200 となる。

図-4 の PLL ループ 応答特性において、N = 200 のボタンをクリックすると その時の ループ特性を見ることができるのだが、ここで Open loop Gain (開ループ・ゲイン) が 変化してしまい カットオフ周波数 fo と その Phase Margin (位相余裕)も変化してしまうことが、すなわち Open loop Gain が大きくなり カットオフ周波数 fo も 150KHz 程 に移動し その時の Phase Margin も 40°程に減少し ループ特性 が不安定の方向にあることが確認できる。

そして、これが ノイズ特性等に大きな影響を及ぼすようであれば、Phase Margin (位相余裕) をもっと大きく取った ループ・フィルター にしたり、 さらに 必要であれば ループ・フィルター を N 値によって切り替えるなどの 回路工夫 が必要となる。

■ 5. PLL 位相雑音 Phase Noise 特性

次に、N = 300 , Phase Margin (位相余裕) 45°で計算した R1=1KΩ, C1=0.0022uF, R2=1.8kΩ, R3=1.2KΩ, C2=560pF の ループ・フィルター を 用いた 3次ループ の Phase Lock Loop に

図-2 に記した VCO. 及び REF. 基準信号の 位相雑音 を与えて、PLL 出力の 位相雑音 C/N.値 の結果を シミュミレーション する。

ここで、青い線 で記したものは VCO.の位相雑音 を オレンジ点線 は 基準信号 REF. の N 倍 悪化した 位相雑音 で あり、黒い線 で記した値(SΦout) が PLL 出力での 位相雑音 を示している。

この シミュレーション 結果から、Phase Margin PM = 45°では カットオフ周波数 fc = 100KHz 付近で ノイズの 数dB の ピークが生じてしまうことが 観測される。

そこで、Phase Margin にもう少し 余裕を持たせることにする。 すなわち、Phase Margin PM = 60°における ループ・フィルター を 再設計する。

ループ・フィルター設計ツール を用いて Phase Margin PM = 60°として 再度 計算し、 定数を追い込むと R1=1.5KΩ, C1=0.0022uF, R2=2.7kΩ, R3=1KΩ, C2=470pF という値となった。

位相雑音 の シミュレーション 結果は、PM = 60° のボタンをクリック すると見れるが、今度は カットオフ周波数 fc = 100KHz 付近で も ノイズの ピークが生じることなく 良好な特性となっていることが確認できる。

このように、PLL の 位相雑音特性は Phase Margin の値に 影響を大きく受けるので、PLL ループ・フィルター の設計を より難しくしている一つとなる。

■ 6. むすび

以上、400 から 600MHz を 2MHz ステップで 可変する 周波数シンセサイザー PLL 回路を 例題として 位相雑音 C/N.値 の 側面から見た 最適な ループ・フィルター

は どのように 選定するのかを考えた。

実際の ループ・フィルター の設計には、オンライン提供している ループ・フィルター設計ツール を用いて計算

し、その使い方の説明も加えた。

そして、PLL ループ 応答特性のシュミレーションによって、分周比 N の変化によって Open loop Gain (開ループ・ゲイン) が

変化してしまい その結果、カットオフ周波数 fo と その Phase Margin (位相余裕)も変動してしまうことを確認した。

さらに、位相雑音 の シミュレーション を通して、Phase Margin の値によって PLL の 出力位相雑音特性にも影響を及ぼすことを説明した。

ここで用いた、ループ・フィルター設計ツール は PLL を 3次ループとして ループ・フィルターを解いているものであり、PLL の設計条件の入力値

に 問題がなければ 正しい値を 算出します。

しかしながら、VCO. 感度の非直線性の問題 や P.Detctor 位相比較器の感度定数等を 正確に見積もることは 難しいことです。

このことや PLL ループ 応答特性 そして 位相雑音 Phase Noise 特性については 今回 結果のみを記したが、その 解析方法等については、別に 記せ

ればと 考えています。

URL : http://gate.ruru.ne.jp/rfdn/