|

PLL �� ��{���� Basic phase lock loop |

BPllNote |

����܂� ���݂ł� PLL (Phase Locked Loop) �� �Z�p�� �e���r�A�p�\�R���A�g�ѓd�b �̂�

�Ȃ炸 �l�X�� ���i�ɗp�����Ă��邱�Ƃ� �����܂ł��Ȃ��B

�܂��APLL �Z�p�̔��W�� PLL ��H�� LSI �� �ɂ���� ��������A���ł� PLL ���ׂĂ̋@�\�� ��� IC �ɓ����Ă���A�u���b�N�{�b�N�X������

����B

����ɁA���g���V���Z�T�C�U �p �� PLL IC �ɂ����Ă� �V���A���f�[�^���͌^ �ƂȂ� ���^�����A������g���� �� GHz �� ���ړ��͂�

���A���[�v�t�B���^ �̒萔�� �ԈႢ�Ȃ����߂�AGHz �т� ���g���V���Z�T�C�U �� ������ ������ �e�Ղ� ��邱�Ƃ�

�\�� ����ƂȂ����B

�������Ȃ���APLL ��H�̈��萫 �� ������� ���g���؊��� �X�s�[�h�A��ʑ��G���A�X�v���A�X�}���x ���� ���\�� �d�v������ ���\���オ �v�X

�v������Ă��Ă��邱�Ƃ������ł���B

�V���O�� ���[�v PLL �ɂ����Ă� ���̍ō����\�� �����o���ɂ� PLL �̍œK�� �v���K�v�ł��邵�A���d���[�v PLL �� �\�z����ɓ������Ă� ����� PLL ��

���Ă� �m�����K�v�ƂȂ�̂� �m���ł���B

�����ł́APLL (Phase Locked Loop) �̓���� ���̒��ŕ`����悤 �ɁA�`�B�� �� �{�[�h���} ��p���� PLL��� �O

�� �����i�K�Ƃ��� PLL �̌������APLL ���\�������H�̓���� �₳���� �������B

�܂� �����g ���g���V���Z�T�C�U PLL �Ƃ��Ă� ��{�����A��{��H�\�� �ɂ��Ă� �q�ׂ�B

���@1. PLL �̊�{�\�� �� ���쌴��

PLL �Ƃ́APhase Locked Loop �̗���ł���A���g�����A�҉�H ���\������B

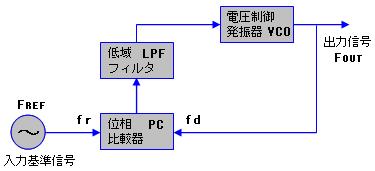

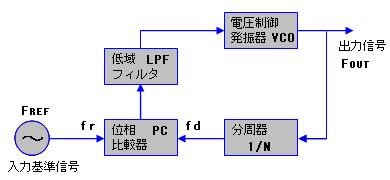

�}-1 �ɂ� ���� ��{�\���} �������B

| |

| �}-1. PLL �̊�{�\���} |

�����ŁAPLL �̊�{����� ���� �� ��������� ���̂悤�ɂȂ�B

1. PLL �� ���b�N���Ă����� fr = fd ���� ���͊�M����� VCO �̏o�͎��g���� �����Ȃ�B

��

2. �ʑ���r�� PC �̏o�͂� �덷�M���p���X �� ��������B

��

3. ���t�B���^ LPF ��ʉ߂��邱�Ƃɂ���� �����d���ƂȂ�B

��

4. ���̒����d���́A�덷�M���ɔ�Ⴕ VCO �̏o�͎��g���� �Ⴍ�Ȃ�l�ƂȂ�B

��

5. VCO �̏o�͎��g���� ������Afr = fd �̏�Ԃɖ߂�B

���̂悤�� PLL �́A��� fr = fd �̏�Ԃ� �ۂ悤�ɓ����Ă���� �D����̂ł���B

�������� ��̓I�� ���������݂�ƁA

| |

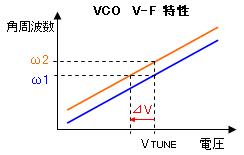

| �}-2. VCO �� V-F���� |

���AVCO �� �� �Ɏ��������� �����Ă���A��M���Ɠ��� ��1 �̎��g���� ���b�N ����A����d���� VTUNE �ƂȂ��Ă���Ƃ���B

���āA���x�ω� �� �o�� �ɂ���� VCO �̓����� �I�����W�� �̂悤�ɕς�����Ƃ���B

����� VCO ����d���� VTUNE �� ��1 �̎��g���� ��2 �� ���� �Ȃ��Ă��܂��B

������ PLL �� ��M���Ɠ��� ��1 �̎��g���� �߂������� �ʑ��덷�d�� ��V �� VCO �ւ� ����d���Ƃ��ĉ��� VCO �̓������ς���Ă� �o�͎��g�����ɁA�������䂵�Ă����B

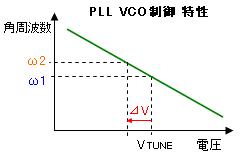

�}-3 �� ���̎��� PLL ��H�� VCO ��������� �}���������̂ŁAVCO �� V-F ���� �� �ɐ��� ���ɂȂ�AVCO �̔��U ���g���𐧌䂷�邱�Ƃ��킩��B

| |

| �}-3. PLL VCO �ւ� ������� |

���@2. PLL �̓���g�`

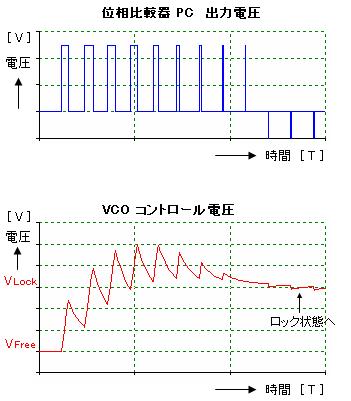

���ɁAPLL �̓���g�`�� ���Ԏ��ł� �������� �l���Č���B

�����ŁA�͂��߂� VCO �� ������g���� ���b�N���ꂸ�� �t���[�������U���Ă���Ƃ���B

������ ��M�����A�t���[�������U��� �������g���� ���͂��ꂽ�Ƃ���B

����� �ʑ���r�� PC �̏o�͂ɂ� �}-4 ��} �̂悤�� �ʑ����ɔ�Ⴕ�� �덷�M���p���X �� ��������B

������ ���̏o�͂� �p���X�I�� �����g�����𑽂��܂�ł���̂ŁA���t�B���^ LPF ��ʂ��� �ϕ�����ƁA�}-4 ���} �̂悤�� VCO �R

���g���[���d���ƂȂ�A���b�N��ԂւƓ������B

���ʂƂ��� VFree �d����� ���{���g ���� VLock �d���� ���b�N��ԂƂȂ�B

| |

| �}-4. PLL �� ���Ԏ����� |

���� ���t�B���^ LPF ���Ȃ���� VCO �́A�덷�M���p���X �ŕϒ����� PLL �� ���b�N��ԂƂ͂Ȃ�Ȃ��B

�܂� LPF �� �萔�� �K�łȂ��Ă��A���b�N��ԂƂȂ�Ȃ��A���b�N��Ԃ� �s����ł���A���b�N��Ԃ܂ł� ���Ԃ������� �Ȃ� �� ���Q�ƂȂ邱�Ƃ� �����ł���B

PLL �ɂƂ��� LPF �̒萔�̐ݒ�A���[�v�t�B���^�̐v �� PLL �̐��\�� ���E���邱�Ƃɂȃ��A�ŏd�v�ƂȂ�B

���@3. PLL ���g���V���Z�T�C�U �̊�{

��������� ���g���V���Z�T�C�U �Ƃ��Ă� PLL ��H�ɂ��� �q�ׂ�B

���g���V���Z�T�C�U ���Ȃ킿 ���g����V���ɍ�� �Ƃ������Ƃł���A�}-1 �� PLL ��{�\���} �� ���g���V���Z�T�C�U ��

�� �����Ȃ������m��Ȃ��B

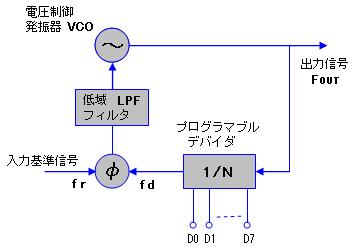

�}-5 �� PLL ���g���V���Z�T�C�U �̊�{�\�� �́A�}-1 �� �d�����䔭�U�� VCO �� �ʑ���r�� PC �̊�

�� ������ 1/N �� �}���������̂ƂȂ��Ă���B

�䂦�� �d�����䔭�U�� VCO �̏o�͎��g���� FOUT �Ƃ���� ���������藧���ƂɂȂ�B

fd = FOUT / N

������ PLL �� �\������邱�Ƃɂ���� fd = fr �������藧�̂�

FOUT = fr �~ N

���ƂȂ�B

���Ȃ킿 �o�͐M�� ���g�� FOUT �́A��M�� ���g�� fr �� N �{�ƂȂ�A���g���V���Z�T�C�U �Ƃ��ē�

�����ƂɂȂ�B

| |

| �}-5. PLL ���g���V���Z�T�C�U �̊�{�\�� |

������ 1/N �� 1/200 �Ƃ���A1MHz �� 200MHz �ɂ��� ���g���V���Z�T�C�U�@�ɂ�� �Ă��{ ��H�邱�Ƃ��ł���B

������ ����x�̈��� LC ���U�� VCO �̏o�͂́A�N���X�^�����U��Ɠ��� ���g������x �ɒu����������̂ł���B

���@4. �v���O���}�u�� �f�o�C�_ ������� PLL ���g���V���Z�T�C�U

���ɁA1/N ������ �� �ϕ����� �v���O���}�u�� �f�o�C�_ �Ƃ��� PLL ���g���V���Z�T�C�U �ɂ��čl����B

��{�` PLL ���g���V���Z�T�C�U �̎��g���W�́A fd = fr �������藧�̂�

FOUT = fr �~ N

�ł������B

�}-6 �Ɏ��� �v���O���}�u�� �f�o�C�_ ������� PLL ���g���V���Z�T�C�U �ŁA���̏�Ԃ��� N �̒l�� 1 �ς���� PLL ���[�v �� �ω����� fd ��

���g���� fr �Ɠ����ɂȂ�悤�ɓ����B

�䂦��

FOUT = fr �~ ( N + 1 )

�ƂȂ�B

���������� �o�͎��g�� FOUT �� ����g�� fr �������ω����邱�ƂɂȂ�B

N �̒l�� ����� 1 �X�e�b�v ���ς��邱�Ƃɂ��Afr �X�e�b�v ������g���V���Z�T�C�U �ƂȂ�B

| |

| �}-6. �v���O���}�u�� �f�o�C�_������� PLL ���g���V���Z�T�C�U |

���̂悤�� PLL ���g���V���Z�T�C�U �� ������ �� �v���O���}�u�� �f�o�C�_ �Ƃ��邱�Ƃɂ���āA���̉��p�͈͂� �傫���L���邱�ƂɂȂ�B

���āA�v���O���}�u�� �f�o�C�_ �� ���W�b�N��H�őg�܂ꂽ �J�E���^��H�ł��邽�߁A���̓�����g���Ɍ��E������A�� GHz �̎��g��

�� ���ڕ��� ���邱�Ƃ͓���B

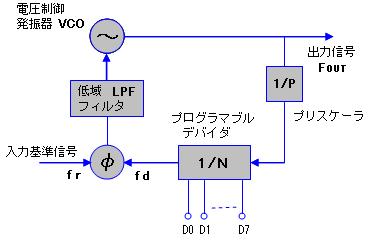

������ �d�����䔭�U�� VCO �� �v���O���}�u�� �f�o�C�_ �̊Ԃ� ���g�����������H�� ���g���ϊ���H��}�����邱�ƂɂȂ�B

�~�L�T ��p���Ď��g���ϊ�������@������̂����A�g���[�h�I�t�I�Ȑ��\�ʂȂǘb�����G������̂ŁA�����ł� �O�u������ �v���X�P�[�� �ɂ��

���@�̏Љ�܂łƂ���B

| |

| �}-7. �v���X�P�[������ PLL ���g���V���Z�T�C�U |

���������� �o�͎��g�� FOUT ��

FOUT = fr �~ N �~ P �ƂȂ�B

���̂悤�� �������삷�� �v���X�P�[�� �� �p���邱�Ƃɂ���� �����g VCO �� �v���O���}�u�� �f�o�C�_ �� �e�Ղ� ���g�� �𐧌�ł���悤�ɂȂ�B

�������A���� �v���X�P�[�� ��}�����邱�Ƃɂ���� ���̖��� �l���Ȃ���Ȃ�Ȃ��B

���Ȃ킿 �v���X�P�[�� ��}�����邱�Ƃɂ���� ���g���X�e�b�v �� �v���X�P�[�� �̕����䕪 �傫���Ȃ�B

�Ⴆ�A�v���X�P�[�� 1/P �� 1/8 ��p�����ꍇ�� ����g�� fr �� 1MHz �Ƃ��� �v���O���}�u�� �f�o�C�_ N �� �l�� 201 , 202 - - - �Ɠ������Ă� �o�͎��g�� FOUT �́A����g�� fr = 1MHz �X�e�b�v �� �V���Z �� �Ȃ炸�Afr �~ 8 = 8MHz �X�e�b�v �ƂȂ��Ă��܂��B

�����A�o�͎��g�� FOUT �� fr = 1MHz �X�e�b�v �Ƃ�������A����g fr �� 1/8 �� 125KHz �� ����悢�̂����APLL �� ��r���g�� fr �� ���������邱�Ƃ� PLL �� �������x �� �m�C�Y �y�� �X�v���A�X���� �ȂǂɂƂ��� �D�܂��� �����ł͂Ȃ��Ȃ�B

�ł́A��������P���邽�߂ɂ� �� �b�� �i��ōs���̂����A���̃m�[�g�ł� ������ �I�� �Ƃ���B

���� �v���X�P�[�������� �����b�g ������ ���� ����g�� fr �� ���������Ȃ��ōς� �v���O���}�u�� �f�o�C�_ �̕������l�Ă���Ă���B

���̕����� �f���A���E���W�����X�E�v���X�P�[�� �܂��� �p���X�E�X���� �����ƌĂ�Ă���B

���̓��쓙�́A�e�N�m�[�g PLL �ɗp���� �v���O���}�u���E�f�o�C�_ �� ����I

���@6. �ނ���

�ȏ�APLL (Phase Locked Loop) �̓���� ���̒��ŕ`����悤 �� PLL �̌������APLL ���\������

��H�̓��� �� ����� ���݂��B

�܂� ���g���V���Z�T�C�U PLL �Ƃ��Ă� ��{����A��{��H�\�� �ɂ��Ă� �������A�v���X�P�[������ �� PLL ���g��

�V���Z�T�C�U �܂� ���_���܂� ���̊T�v���L�����B

PLL ���g���V���Z�T�C�U�p LSI �̐i�W�ɂƂ��Ȃ��A�����g�� PLL ���g���V���Z�T�C�U �̐v���e�ՂɂȂ�܂����B

�����āAPLL ��H�̈��萫 �� ������� ���g���؊��� �X�s�[�h�A��ʑ��G���A�X�v���A�X�}���x ���̐��\�� �d�v������ ���\���オ �v�X�v������

�Ă��Ă��錻�݁A���̍ō����\�������o���ɂ� PLL �̍œK�� �v���d�v�ł���A����ɂ� PLL �ɂ��Ă� ��������Ƃ��� ��{�m���� �K�v�ł���

���Ƃ� ������ �����ł��B

URL : http://gate.ruru.ne.jp/rfdn/