|

ver.03 | |

�ʕ��i�Őv���� PLL ���g���V���Z�T�C�U |

||

| �� �戵������ INSTRUCTION MANUAL | TrPllManu | |

| RDN-TR01S PLL�V���Z/ RDN-TR01X ������� | ||

�܂����� PLL ( Phase Locked Loop )�Z�p�́C���g���V���Z�T�C�U �Ƃ��� �}���ɕ��y���C�q���ʐM��

�g�ѓd�b�Ȃǂ̑����̖����@�� �ɂƂǂ܂炸�C�l�X�ȕ���̐��i�Ɂ@�p�����Ă��܂��D

�����āC�������ʑ���r�����̉����� ���g���V���Z�T�C�U�p�� LSI ���J������C���ł� �V���A���f�[�^���͌^�ƂȂ� �����^������A��GHz ��

���g���V���Z�T�C�U �� ���i�_���� ���Ȃ��\���ł��鎞��ƂȂ��Ă��܂��D

������ ���̔��ʁCPLL �Z�p���w�т����Ǝv���҂ɂƂ��ẮCPLL �� �u���b�N�{�b�N�X�� ���Ă��܂��X�̉�H�̓�������ۉ�H��ʂ��� �c������

���Ƃ�����Ȃ��Ă��邱�Ƃ� �����ł�.

���� RDN-TR01S PLL�V���Z �� RDN-TR01X ��������́C�g�����W�X�^�Z�p�� 2006�N 3���� �` �uPLL���g���V���Z�T�C�U�̐v�@�O�����v

�Ƒ肵���A�ڋL�������M�����ŏ����������̂ŁCPLL ���g���V���Z�T�C�U �� ���쌴����e�Ղɗ����ł���悤�ɁC�������ʑ���r��� �ʕ��i��

�v���C�܂� VCO �ɂ� �����\�� 180 - 360MHz �� ���[�m�C�Y�C�I�N�^�[�u�L�ш攭�U��𓋍ڂ��邱�ƂŁC�l�X�� PLL �̎����� �e���̔g�`�� �m�F���Ȃ���i�߂�

���Ƃ��ł��� ������ �u���b�h�{�[�h�\�� PLL ���g���V���Z�T�C�U �ł��D

PLL�Z�p�̊�b ������ ���p�ւ� ���� �g���[�j���O �{�[�h �� ���낢��ƍH�v����� �g�p���Ē�����Ǝv���܂�.

������� �g���[�j���O �{�[�h �Ƃ��Ă̎g�p�݂̂Ȃ炸�C���p��H�ւ̉��p�C�Ⴆ�� 500KHz �� ��M������͂��� 180 - 360MHz �Ԃ� 4MHz �X�e�b�v��

�V�O�i���\�[�X�Ƃ��āC5MHz �� ���[�m�C�Y��M�� �� ���͂��� 200MHz �ւ� ���[�m�C�Y �Ă��{��H �ȂǂƂ��āC�����g�N���b�N�̍쐬�ɂ� ���g�p�ɂȂ�܂�.

���@�ڎ�

���@1. PLL ���g���V���Z�T�C�U�� �u���b�N�} �� ���쌴��

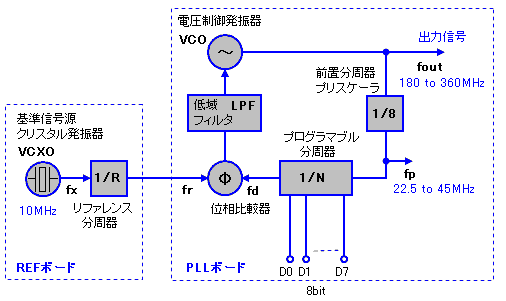

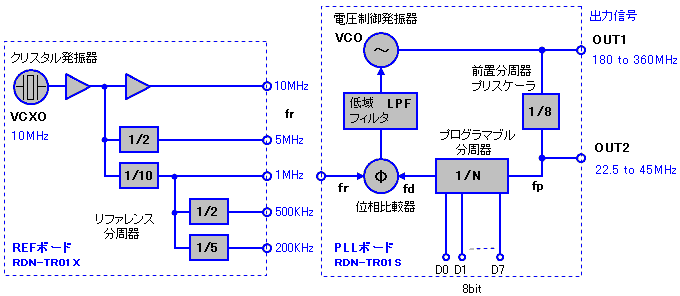

�} 1 �� �g���[�j���O �{�[�h �ɑg�ݍ��܂�Ă��� PLL ���g���V���Z�T�C�U �� �u���b�N�} �������܂�.

| |

| �}-1. PLL���g���V���Z�T�C�U�̃u���b�N�} |

�} 1 ��PLL ��H�� ���Ȃ��\�������� PLL �� ��� �ʑ����g����r�� PFC �ɓ��͂���� fr �� fd�� ���� ���g���� �����ʑ��ɂȂ�悤�� �����܂�.

���Ȃ킿 fr = fd - - - - - (1)

�Ƃ����W����ɐ��藧���܂�.

���� �v���O���}�u�������� 1/N �� ���͎��g�� fp �� �l�����

fp = fr �~ N - - - - - (2)

�ƂȂ�܂�.

������ �v���O���}�u��������� CMOS���W�b�N�J�E���^ �ɂ���č\������,���̓�����g���� 50MHz���ł���C�����g�̓d�����䔭�U��VCO �̏o�͂ڂɕ������邱�Ƃ��ł��܂���D

�����ŁCVCO �� �v���O���}�u��������̊Ԃ� �������삷�� �O�u������C�����ł� 1/8 �� �v���X�P�[���i�O�u������j���}������Ă��܂��D �䂦�� �o�͐M����

fvco = fr �~ N �~ 8 - - - - - (3)

�̊W�ƂȂ�܂�.

RFDN�z�[���y�[�W��� PLL�̓��쌴���� �₳����������� �e�N�m�[�g �uPLL �� ��{����v ���������܂����̂ŁC�������������I

���@2. ���\ �y�� �d�l

�� PLL�{�[�h RDN-TR01S| �E ���g���͈� | OUT 1 �F | 180 - 360MHz | |

| OUT 2 �F | 22.5 - 45MHz | ||

| �E ���g������\ | OUT 1 �F | fr�~8 | |

| OUT 2 �F | fr | ||

| �E ��M�� fr | 10MHz��fr | ��180KHz |

| �E �o�̓��x�� | OUT 1 �F | ��-2dBm | |

| OUT 2 �F | ��+2dBm |

| �E �ʑ��G�� | OUT 1 �F | ��-100dBc/Hz | �i240MHz�o�́C4MHz�X�e�b�v�C10KHz�I�t�Z�b�g�j | |

| �i����m�C�Y�͗��z�j | �Q�l�f�[�^ | |||

| OUT 2 �F | ��-118dBc/Hz | �i30MHz�o�́C500KHz�X�e�b�v�C10KHz�I�t�Z�b�g�j |

| �E �d���d�� | �}12V | �C+5V |

| �E ���g���ύX���@ | 8bit �f�B�b�v�X�C�b�`�ɂ� |

| �E ���o�̓R�l�N�^ | SMB �i50���j |

�� REF�{�[�h RDN-TR01X

| �E �o�͎��g�� | 10MHz�C5MHz | �C1MHz�C500KHz�C200KHz | |

| �E ���g������x | ���}50ppm | �iat 0�`40���j | |

| �E ���g���ϔ͈� | ���}100ppm | �i3.5V�}2V�j |

| �E �o�̓��x�� | ��-2dBm |

| �E �d���d�� | +12V | �C+5V |

| �E ���g���������@ | VR�ɂ� |

| �E �o�̓R�l�N�^ | SMB �i50���j |

* ���g������x�͎���@�ł̕]���ł��D

���@3. �{�[�h�̊O�ςƐڑ�

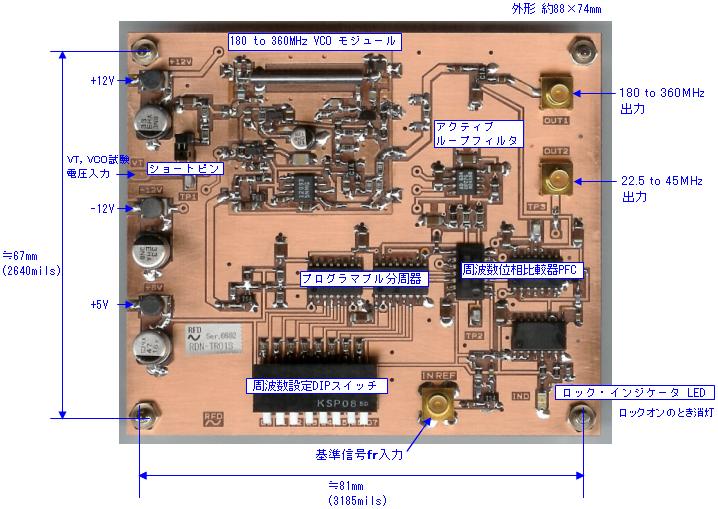

�� PLL�{�[�h RDN-TR01S

|

| �ʐ^-1. 180 to 360MHz PLL�{�[�h�̊O�� |

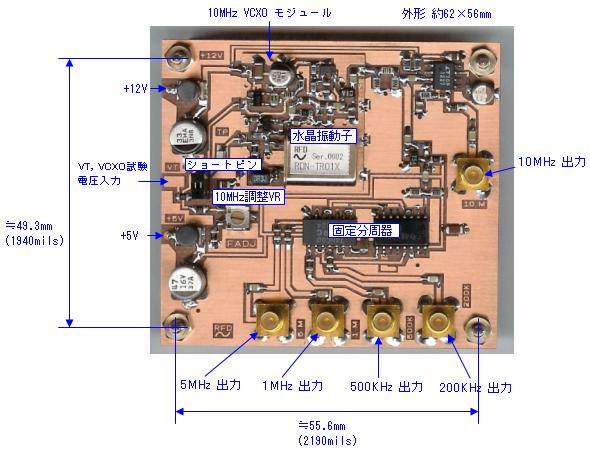

�� REF�{�[�h RDN-TR01X

|

| �ʐ^-2. 10MHz VCXO REF�{�[�h�̊O�� |

�� PLL�{�[�h��REF�{�[�h�̐ڑ�

|

| �ʐ^-3. PLL�{�[�h��REF�{�[�h�̐ڑ� |

���@4. PLL ���g���V���Z�T�C�U���\�������H

�����ł́CPLL ���g���V���Z�T�C�U���\������ �X�̉�H�� ���쌴�� ���ȒP�� �q�ׂ܂��D

�i�v���@���܂߁C�ڂ����́C�g�����W�X�^�Z�p���ɋL���܂��̂� ��낵�����肢���܂��j�D

�@ �d�����䔭�U�� VCO ( Voltage Controlled Oscillator )

�d�����䔭�U�� VCO �́C���̖��̂Ƃ��� �����d���Ŕ��U���g���𐧌䂷���H�ŁC���g���V���Z�T�C�U �Ƃ��ėv���������g���͈͂� VCO ��

���U�ł��Ȃ���� PLL �͍\���ł��� PLL���g���V���Z�T�C�U�̒��S�ƂȂ镔���ł��D

PLL ��H�ɂ����� VCO �̓����́C��ʂ� �ȉ��̐��\���d�v������܂��D

(a)�@�K�v�Ȏ��g���͈͂��\���� �J�o�[�ł��锭�U�ш������Ă��邱��

(b)�@���x��d���̕ϓ��ɑ��� ���g������x���悢����

(c)�@�m�C�Y������X�v���A�X�����Ȃ�����

(d)�@����d���ɑ��锭�U���g���̒��������悢����

�����ŁC(b) �̍��ڂɂ��Ă� VCO �̉��x��d���ϓ��ɂ����g���ω��� PLL ���\�����邱�Ƃɂ���� �z���C���P

����̂ł����C����ɂ����E������C���܂�ɂ����g������x�������ƁCPLL �ɂ�鐧��d�����L���i�d���d���܂Łj�ł��̂ŁC����ȏ�� VCO ��

�����Ă��܂��� ���b�N���n�Y���Ă��܂� PLL ���\���ł��Ȃ��Ȃ�܂��D

�܂��C(c) ���ɂ��Ă� VCO �m�C�Y�� PLL ���\�����邱�Ƃɂ��C���[�v�ш���ŗ}��������P�ł��܂����C���Ƃ̃m�C�Y�������傫����� ���P

���ʂ͌������܂��D

(d) ���ɂ��ẮC�������������� PLL�̃m�C�Y�����ɉe�����܂����C���� PLL �� FM �ρE�����Ƃ��ėp����ꍇ�ɍł��d�v�ȓ����ƂȂ�܂��D

| |

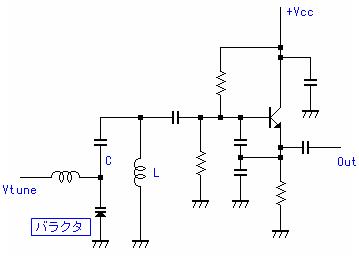

| �}-2. �R���s�b�c�^ VCO ���f�� |

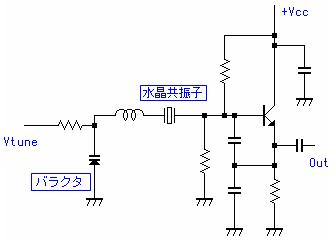

�}-2 �� �����g�ł̓d�����䔭�U�� VCO �̉�H��ł����C������ L C �� �^���N��H�̈ꕔ�� �ϗe�ʃ_�C�I�[�h�� �p���邱�Ƃɂ���� LC������H�� �o���N�^ �ɓ��͂���� Vtune ����d���ɂ���āC���U ���g���U���g�����ς��Ă��܂��D

����d�� Vtune �� �v���X�����ɑ����Ă����� �o���N�^ �̐ڍ��e�ʂ� �������Ȃ�A���ʂ� ���� VCO �� ���U���g���� �����Ȃ�܂��D

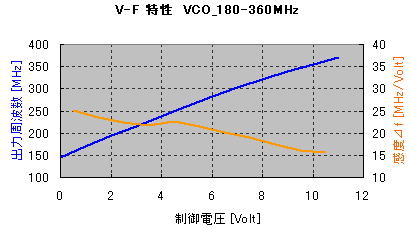

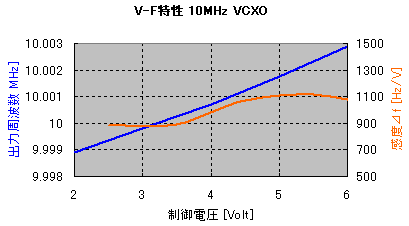

�}-3 �ɂ� VCO �� ����d�� �� ���U���g�� �����CV-F ���� ���L���܂�.

| |

| �}-3. �����g VCO �� V-F ��\���� |

�������C���ۂ� VCO �� V-F ������ ���̂悤�Ɉ꒼���łȂ��C�I�����W�_�� �ŋL�����悤�� �d���͈͂� ����� ���g���Έ� ��f �� �قȂ��Ă��܂��܂��D

�����āC���̂��Ƃ� VCO �̊��x�� ���U���g���ɂ���� �قȂ�Ƃ������ƂŁCPLL �̃��[�v�����ɉe�����y�ڂ��܂��D �܂��C�L�ш� ���U��ɂȂ�Ȃ�ق� �ʏ� ���̓����͈������܂��̂ŁCPLL�̐v����������܂��D

| |

| �}-4. 180 to 360MHz VCO �� V-F ������ |

�����ŁC���U���g���� 200MHz �t�߂ł� V-F ���� �� 22.5MHz/Volt ���ł����A���U���g���� 350MHz �t�߂ɂȂ�܂��� 15.5MHz/Volt �܂� �c�O�Ȃ��犴�x�������Ă��܂��D

�A �d�����䐅�����U�� VCXO ( Voltage Controlled Crystal Oscillator )

PLL���g���V���Z�T�C�U�o�͂̎��g������x�́C��M�� fr �̒l�Ō��܂�܂��D �ł�����C���g��

����x�̗D�ꂽ�������U���p���邱�ƂɂȂ�܂��D

�����āC���g���̒����ɂ́C�ȑO�̓g���}��p���郁�J�j�J���`���[�j���O�ł������C���͓d�q�`���[�j���O�����߂��܂��̂ŁC�d�����䐅��

���U�� VCXO �Ƃ������̂�p����̂���ʂł��D

����ɁC�������U��̉��x�ω��ɂ����g���Y����⏞���� TCXO�iTemperature Compensated Crystal Oscillator�j�� �������U�q�̉��x����Ɉ���

�Ȃ�悤�ɃI�[�u��������Ď��g�������艻������ OCXO�iOven Controlled Crystal Oscillator�j������܂��D

| |

| �}-5. �R���s�b�c�^ VCXO ���f�� |

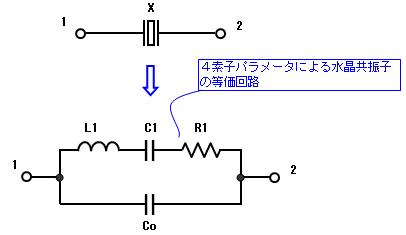

�����ŁC�������U�q��d�C��H�Ƃ��ē�����H�ɒu��������ƁC�}-6 �̂悤�ɕ\�����Ƃ��ł��܂��D

���Ȃ킿�C2�[�q�Ԃ̃C���s�[�_���X�������Ƃ��������Ȃ钼�U���g��fs �� ���ɂ����Ƃ��傫���Ȃ���U���g��fp ������ ���܂����C�������U�q�ł� fp-fs �Ԃ̂킸���ȕ������U����L�ƂȂ��Ă��āC���U��Ƃ��ăC���_�N�e�B�u�ɓ��삷�邱�ƂɂȂ�܂��D

�����āC�����̂pu�l�i�����ׂp�j�́C��ʂɐ������琔�\���̔��ɑ傫�Ȓl�ƂȂ�C���肵�����g���ƒ�ʑ��G���̔��U��ݏo���Ă����̂ł��D

| |

| �}-6. �������U�q�̓�����H |

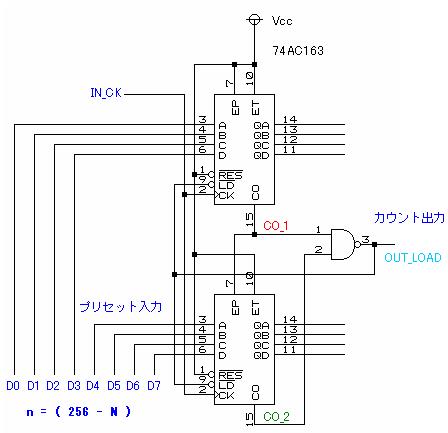

�B �v���O���}�u�������� �� �v���X�P�[��������

�v���O���}�u�������� �� ������N �� �ݒ肷�邱�ƂŁC�V���Z�T�C�U�̏o�͎��g�����ς��邱�Ƃ��ł��܂��D

���ł́CPLL IC �`�b�v �̒��� �v���X�P�[�� + �v���O���}�u�������� ���g�ݍ��܂�Ă��āC�V���A���R���g���[�� ����� ������N ��ݒ��

���鎞��ƂȂ��Ă��܂�. �������C�����ł� CMOS ���W�b�N �J�E���^ IC �ɂ� 8 bit �v���O���}�u��������� �g��ł��܂�.

| |

| �}-7. 8bit �v���O���}�u�������� |

4 bit �����J�E���^ �ł��� 74AC163 �� 2 �� �� �c��ڑ����܂���.

�ݒ肵�� D0 �` D7 �� �f�[�^ ���� �A�b�v�J�E���g���� ��̃p���X���o�͂��܂��D �ł�����C�v���O���}�u�������� �Ƃ��Ă� N �̒l�� D0 �` D7 �� �ݒ肷�� �f�[�^ n �́C�����̊W�ƂȂ�܂��̂� ���ӂ��ĉ������D

n = ( 256 - N ) - - - - - (4)

���ɁC���̃v���O���}�u��������̓���ł�����g���� AC �^�C�v �� �����̉�H�H�v�����Ă� �� 50MHz �قǂƂȂ��Ă��܂��D

�����ŁC180 - 360MHz �� VCO �o�͂� �v���O���}�u���������邽�߂ɂ� �������g�����ł��鍂���� �O�u������C�v���X�P�[�� �� �K�v�ƂȂ�܂��D

�����ł� 1/8 �̃v���X�P�[�� �𓋍ڂ��C180 - 360MHz �� 22.5 - 45MHz �Ƃ��Č�i�� �v���O���}�u�������킪����ł�����g���ɗ��Ƃ��Ă��܂��D

���̂悤�� �������삷�� �v���X�P�[�� �� �p���邱�Ƃɂ���� �����g VCO �� �v���O����������ŗe�Ղ� ���g���𐧌�ł���悤�ɂȂ�܂����C���ƂȂ� ���̓_�� �l�����Ȃ���Ȃ�܂���D

���Ȃ킿�C�v���X�P�[�� ��}�����邱�Ƃɂ���� ���g���X�e�b�v �� �v���X�P�[�� �̕������Ԃ�C���̏ꍇ�ł��� �W �{ �ɂȂ��Ă��܂����Ƃł��D

�Ⴆ�C����g�� fr �� 500KHz �Ƃ��� �ꍇ�Cfp�i22.5 - 45MHz�o�́j�ł� 500KHz �ƂȂ�܂����C�o�� fvco�i180 - 360MHz�o�́j �ł� ���� �W �{ �� 4 MHz �X�e�b�v ��

�Ȃ��Ă��܂��܂��D

�ł�����C�o�� fvco �� 500KHz �X�e�b�v �ɂ�������Afr �� 1/8 �̎��g���ɂ���悢�̂ł����C��r���g���� �Ⴍ�Ȃ�� PLL �� �������x�� �m�C�Y �y�� �X�v���A�X�����Ȃǂ�

�Ƃ��� �D�܂��������łȂ��Ȃ�C���[�v�����̐v�������܂��D

�C ��M�����C���t�@�����X������

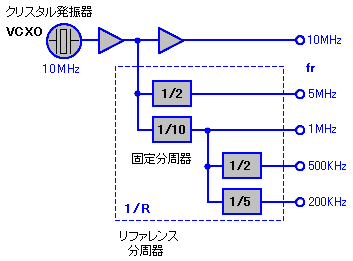

10MHz VCXO ����Ȃ��M��������PLL�̊���g�� fr �Ƃ��郊�t�@�����X������́C�����ł� �}-8 �Ɏ����\���Ƃ��܂����D

| |

| �}-8. ���t�@�����X������̍\���} |

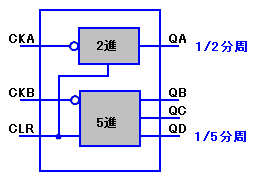

������ �}-9 �ɂ́C74xx390�̓����\���������܂����C2�i��5�i�̃J�E���^���������Ă��܂��̂ŁC�������c��ڑ����邱�Ƃɂ���ĊȒP�ɔ�10�i �J�E���^���i1/10�����j���邱�Ƃ��ł��܂��̂ŁC�����p���܂��D

| |

| �}-9. 74xx390�̓����\���} |

�D �ʑ����g����r�� PFC ( Phase Frequency Comparator )

PLL ��H���\������ʑ���r��́C���݂ł� �ʑ����g����r��PFC�iPhase Frequency Comparator�j�C�������͈ʑ����g�����g��PFD�iPhase Frequency Detector�j��

�Ă��f�W�^���^��r�킪���p����Ă��܂��D

���̕����̔�r��́C�P�T�C�N���ȓ��ł��ʑ���r�������Ȃ��ʑ����ɔ�Ⴕ���o�͓d�������C����ɂP�T�C�N���ȏ�ł����g����r�Ƃ���

�����C���g�����ɔ�Ⴕ���d�����o�͂���Ƃ����Q�̋@�\���������킹�Ă��܂��D

�ł�����CVCO�̎��g�����v���`���[�j���O���ă��b�N���ׂ����g���ɗU�����邱�ƂȂ��m���Ƀt�F�C�Y���b�N�ł���̂ł��D

���� PFC �̓o��ŁCPLL�̎��g���V���Z�T�C�U�Ƃ��Ẳ��p���傫���L����܂����D

| |

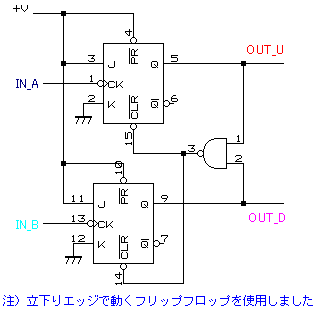

| �}-10. �ʑ����g����r��PFC�̍\���} |

�����ł́C�f�B�X�N���[�g���W�b�NIC��p���� �}-10 �ɋL���Q�̃t���b�v�t���b�v�ƃi���h��H��g���킹�� PFC ������Ă��܂��D

�ʑ����g����r�� PFC �̓���ɂ��ẮCRFDN�z�[���y�[�W��̃V���[�g�m�[�g �uPLL�ʑ���r��̓���v �ŁC����� �̓���g�`�^�C���`���[�g���L���ďڂ����������Ă��܂��̂ŁC�������������I

�E ���[�v�t�B���^ �܂��� ���[�p�X�t�B���^ LPF

�ʑ����g����r�� PFC �œ���ꂽ�ʑ����p���X�ɑ��āC���j�A �ɕω�����d���ɕϊ����邽�߂ɁC�`���[�W�|���v��H + LPF �̍\��

�����̂���ʓI�ł����CPFC ��U�CD�o�͂�OP�A���v�̍������͂ɂȂ��ŗp������@������܂��D ���̕���

�ł���OP�A���v�́C�R�X�e�[�g�ւ̕ϊ��Ɠ����ɁC�ϕ���i�A�N�e�B�u�t�B���^�j�Ƃ��Ă������C�T���v���E�z�[���h�@�\�����s���܂��D

�ŋ߂ł́COP�A���v�̎��g�������ɉ����C�m�C�Y������[�N�d�������Ȃǂ̐��\�����サ�Ă��܂��̂ŁC���̕������g���Ղ��Ȃ��Ă��܂�.

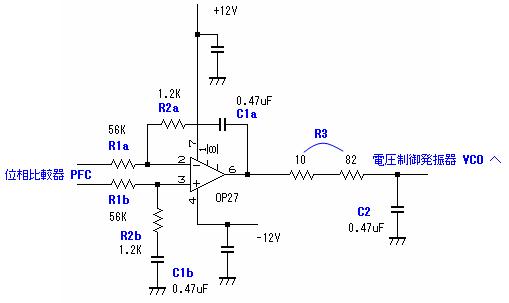

�܂��C�`���[�W�|���v��H���ʂɑg�ނƕ��i�̓_���������܂��̂ŁC�����ł� ����OP�A���v��p���������Ń��[�v�t�B���^��g�݂܂��D

| |

| �}-11. �A�N�e�B�u LPF �ɂ�� ���[�v�t�B���^ |

�L������Ă����R �y�� �R���f���T�̒l�́C����g�� fr = 500KHz �� �o�͎��g�� fout = 180MHz �̏ꍇ�ɁC�J�b�g�I�t���g�� fo = 1KHz �� ���Čv�Z���ꂽ�l�ł����C����ɂ��Ă� 8. �œK�� ���[�v �t�B���^ �萔 �� ���� �ŏq�ׂ܂��D

���@5. ������@ �iPLL���g���V���Z�T�C�U�����j

�����ł� PLL���g���V���Z�T�C�U�̏o�͎��g���� �ݒ肷��菇 �� 5�̗Ⴉ��������܂��D

| |

| �}-12. RDN-TR01S PLL�V���Z/ RDN-TR01X �N���X�^������̊�{�\�� |

�i �ʐ^-3. PLL�{�[�h��REF�{�[�h�̐ڑ� ���Q�l�ɂ��� SMB�P�[�u����ڑ����������D�@�܂��C�d���d�����ԈႦ�Ȃ�

�悤�ɋ������Ă������� �j�D

�@�@��M�� fr = 500KHz �� �o�͐M�� fout = 180MHz

�o�͐M�� fout = 180MHz ��ɂ� �v���O���}�u�������� �ւ̓��͎��g���� fp = 22.5MHz �ƂȂ�܂��D

�䂦�� fr = fd = 500KHz �ł��̂� N �́C

N = 22.5 / 0.5 = 45 �ƂȂ�܂��D

���������āC�v���O���}�u�������� ��ݒ肷�邽�߂� n �́C

n = ( 256 - N ) = 211 �ƂȂ�܂��D

�i �B �v���O���}�u�������� �̓���������Q�Ƃ������� �j

2�i���Ƃ��āC

211 dec = D3 hex = 1101 0011 bin �� �f�B�b�v�E�X�C�b�` �ɂĐݒ肵�܂��D

�iD0�̈ʒu���ԈႦ�Ȃ��悤�ɁC���̎ʐ^���Q�l�ɂ��Ă��������I�j

| |

| �ʐ^-4. n=211 �f�B�b�v�E�X�C�b�` �̐ݒ� |

�A�@��M�� fr = 500KHz �� �o�͐M�� fout = 360MHz

�o�͐M�� fout = 360MHz ��ɂ� �v���O���}�u�������� �ւ̓��͎��g���� fp = 45.0MHz �ƂȂ�܂��D

�䂦�� fr = fd = 500KHz �ł��̂� N �́C

N = 45.0 / 0.5 = 90 �ƂȂ�܂��D

���������āC�v���O���}�u�������� ��ݒ肷�邽�߂� n �́C

n = ( 256 - N ) = 166 �ƂȂ�܂��D

2�i���Ƃ��āC

166 dec = A6 hex = 1010 0110 bin �� �f�B�b�v�E�X�C�b�` �ɂĐݒ肵�܂��D

�B�@��M�� fr = 10MHz �� �o�͐M�� fout = 240MHz

�o�͐M�� fout = 240MHz ��ɂ� �v���O���}�u�������� �ւ̓��͎��g���� fp = 30.0MHz �ƂȂ�܂��D

�䂦�� fr = fd = 10MHz �ł��̂� N �́C

N = 30 / 10 = 3 �ƂȂ�܂��D

���������āC�v���O���}�u�������� ��ݒ肷�邽�߂� n �́C

n = ( 256 - N ) = 253 �ƂȂ�܂��D

2�i���Ƃ��āC

253 dec = FD hex = 1111 1101 bin �� �f�B�b�v�E�X�C�b�` �ɂĐݒ肵�܂��D

�C�@��M�� fr = 200KHz �� �o�͐M�� fout = 200MHz

�o�͐M�� fout = 200MHz ��ɂ� �v���O���}�u�������� �ւ̓��͎��g���� fp = 25.0MHz �ƂȂ�܂��D

�䂦�� fr = fd = 200KHz �ł��̂� N �́C

N = 25.0 / 0.2 = 125 �ƂȂ�܂��D

���������āC�v���O���}�u�������� ��ݒ肷�邽�߂� n �́C

n = ( 256 - N ) = 131 �ƂȂ�܂��D

2�i���Ƃ��āC

131 dec = 83 hex = 1000 0011 bin �� �f�B�b�v�E�X�C�b�` �ɂĐݒ肵�܂��D

�D�@��M�� fr = 5MHz �� �o�͐M�� fout = 200MHz

�o�͐M�� fout = 200MHz ��ɂ� �v���O���}�u�������� �ւ̓��͎��g���� fp = 25.0MHz �ƂȂ�܂��D

�䂦�� fr = fd = 5MHz �ł��̂� N �́C

N = 25.0 / 5.0 = 5 �ƂȂ�܂��D

���������āC�v���O���}�u�������� ��ݒ肷�邽�߂� n �́C

n = ( 256 - N ) = 251 �ƂȂ�܂��D

2�i���Ƃ��āC

131 dec = 83 hex = 1111 1011 bin �� �f�B�b�v�E�X�C�b�` �ɂĐݒ肵�܂��D

���@6. 10MHz VCXO �̎��g�������ɂ���

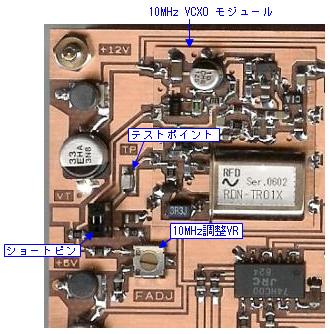

10MHz VCXO REF�{�[�h�ɂ́C�ʐ^-5 �Ɏ����悤�� 10MHz VCXO �����g�������p�� VR ������܂��D

| �e�X�g�|�C���̓d�� ��+3.16V |

|

| �ʐ^-5. 10MHz VCXO �̎��g�������p VR |

| |

| �}-13. �� V-F ������ |

VR �ɂ�� VCXO �ւ̐���d���̉ϔ͈͂́C+3.0V�`+3.6V �قǂƂȂ��Ă��܂��D�@�ł�����C10MHz-20ppm�C10MHz+40ppm �قǂ͈̔͂� �ςł��܂��D�@�i�V���g�s�����āCVT �[�q�ɊO������d������������� VCXO ���L���͈͂Ő��䂷�邱�Ƃ��ł��܂��j�D

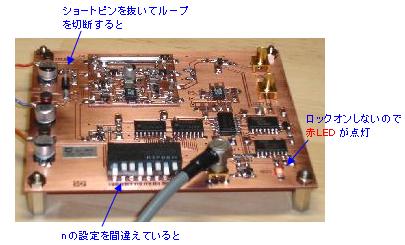

���@7. ���b�N�C���W�P�[�^�ɂ���

180 to 360MHz PLL�{�[�h�ɂ́C�ʐ^-6 �Ɏ����ʒu�� LED �� ���b�N�E�C���W�P�[�^��H�ƂȂ��Ă��܂��D

| |

| �ʐ^-6. ���b�N�E�C���W�P�[�^��H |

�����ŁCPLL���`������Ă��Ȃ��ꍇ�� ��LED ���_�����Čx�����܂��D

�Ȃ��C���b�N�C���W�P�[�^��H�� �ʑ����g����r�� PFC �̏�Ԃ��i�p���X�̗L���j���Ă��܂��̂ŁCPFC �Ɋ�M�� fr �� ���͂���Ă��Ȃ��Ɠ��삵�܂���D

���@8. �œK�� ���[�v �t�B���^�萔 �� ����

PLL���g���V���Z�T�C�U�� �œK�����[�v �t�B���^�萔 �����߂邱�Ƃ� ����ł��D�@�����ł� �ȒP�ȏЉ�ƁC

�M�҂� �z�[���y�[�W��� PLL �� 3�����[�v �Ƃ����ꍇ�� �v�c�[�� ���������Ă���܂��̂ŁC

�����p���� ���[�v �t�B���^�萔 �����߂�菇���L���܂��D �i�ڂ����́C�g�����W�X�^�Z�p���ɋL���܂��̂� ��낵�����肢���܂��j�D

PLL �� �ʑ��C���g���Ɋւ��� �t�B�[�h �o�b�N ���[�v�C���A�҂̃��[�v �� �\������Ă��܂��D�@�ł�����C�����͂ɂ� ���t�B�[�h �o�b�N ���_���p�����܂��D

�}-14 �� ���`���f�������� PLL �̊�{�\���} �� ���� �u���b�N���} �������܂��D

| |

| �}-14. PLL�̊�{�\���} �� �u���b�N���} |

������ �I�[�v�� ���[�v �Q�C���C�ꏄ�`�B�� G(s)�EH(s) �� ����킷�ƁC

G(s)�EH(s) = K �E F(s)/s �ƂȂ�܂��D

������ K �́C

K = Kp �E Kv / N

Kp �F �ʑ���r��� ����

Kv �F VCO �� �ϊ�����

N �F ������

�ł�����C�ʑ���r��̗��� Kp�CVCO �� �ϊ����� Kv �y�� ������ N �� ���߁CF(s) �Ɏg�p���� �t�B���^ �� �`�B�� �����ĉ����C �t�B���^ �̒萔�邱�Ƃ��ł��܂��D

�z�[���y�[�W�� �� �v�Z�c�[�� �ł́C3��PLL �Ƃ��Ă� LPF �� �`�B�� �� F(s) �Ƃ��� �����Ă��܂��D

���@Kp�CKv�CN�C������ fo �ƃ�o �����߂�

�ł́C�o�k�k ���g���V���Z�T�C�U ��H�� Kp , Kv ������ N ����C�K�v�Ƃ��� PLL������ ���� �t�B���^�CLPF �� �萔�� ���߂Ă݂܂��傤�D

�@�@�ʑ���r��� �����萔�@Kp

�ʑ���r��ɂ� �d���o�͌^ �� �d���o�͌^ ������C���̒P�ʂ� [ V/rad ] �y�� [ A/rad ]�ł��邱�Ƃ��� �킩��悤�� 1���W�A�� ����

�� �d�� �������� �d���l�ƂȂ�܂��D

�g���[�j���O �{�[�h �Ɏ��߂�ꂽ��H�����ł���,

Kp = Vo / 2��

[ V/rad ]

�� 0.79

( Vo �� CMOS �o�͓d���� �����ł� +5V �Ƃ��� )

�ƂȂ�܂��D

�A�@VCO �� �ϊ������@Kv

VCO �� �ϊ������́C

Kv = (��f / ��V) �E 2��

[ rad/s/V ]

�����狁�܂�܂��D

�v�Z�c�[�� �ł� VCO ���x Fv �� ���͂��邩���� �ƂȂ��Ă��܂��D

Fv = ��f / ��V

[ Hz/V ]

�����ł� �}-4 �� 180 - 360MHz VCO�@V-F ���� ��� ���ϓI�Ȓl�Ƃ��āC

Fv �� 20

[ MHz/V ]

�Ƃ��܂����D

�B�@������ N

���� ������ N �̒l�ł����C�����ł� ����g�� fr = 500KHz �� �o�͎��g�� fout = 180MHz �̒l�Ƃ��܂��D

N = 180MHz / 500KHz

= 360

�C�@�J�b�g�I�t���g�� fo

PLL �� �J�b�g�I�t���g�� fo �́C�I�[�v�� ���[�v ���� �� �Q�C�� �� 1 �ɂȂ���g���ł��D�@������ �ʑ��G�������́C���̎��g����� �Ⴂ

���g�� �ł� ��M���ɂ�� �ʑ��G���� �x�z�I�ɂȂ�C���̎��g����� �������g���ł� VCO �� �ʑ��G���� �x�z�I�ɂƂȂ�܂��D

RFDN�z�[���y�[�W��� �ʑ��G�� C/N �̑��ʂ���݂� �œK�� PLL �J�b�g�I�t���g���� �ǂ̒l�Ɍ��߂邩�� �₳����������� �e�N�j�J���E�m�[�g �uPLL ���[�v�E�t�B���^�̐v���@�v ���������܂����̂ŁC�������������I

�܂��C�ړI�ɂ���Ă� �J�b�g�I�t���g�� fo �̒l�� �ʑ��G���̑��ʂ��猈�肷��̂ł͂Ȃ��C�X�v���A�X�̏����� �����X�s�[�h ���猈�߂�ꍇ������܂��D

�����ł́C�J�b�g�I�t���g�� fo = 1KHz �Ƃ��� �v�Z���܂��D

�D�@�ʑ��]�T ��o

���̒l�ɂ���āC���A�҉�H�̈��萫�� ���肳��܂��D

PLL �� �J�b�g�I�t���g�� fo�C���Ȃ킿 �I�[�v�� ���[�v ���� �� �Q�C�� �� 1 �ɂȂ���g���ŁC���A�҂��Ĕ��U���Ă��܂� �ʑ� 180������ �ǂ̒��x�̗]�T�����邩��\���Ă��܂��D

�ł�����C���̈ʑ��]�T�� ���Ȃ��� ���[�v ������ �s�[�N ���C�ʑ��G�������ɑ傫�Ȃ���オ�肪�����Ă��܂��܂��D

�ʏ� ���̗]�T�� 45���ȏ�����܂����C�����ł� �ʑ��]�T ��o = 60���Ƃ��� �v�Z���܂��D

���@PLL�v�Z�c�[���ɂă��[�v�t�B���^�萔�����߂�

�z�[���y�[�W�� �� PLL �v�Z�c�[�� �ɂāC3��PLL�Ƃ��Ă� ���[�v�t�B���^�萔 �����߂邱�Ƃ��ł��܂��D

�n�߂ɁCPLL ���[�v �t�B���^�̐v �c�[�� �� ��ʂ� ��ŋ��߂� �e�l����͂��܂��D

| |

| �}-15. PLL�v�c�[�����͉�� |

�}-15 �Ɏ����悤�� �e �v�����̒l�� ���͂��� START �������܂��D

��

| |

| �}-16. �A�N�e�B�u�E���[�v�t�B���^�̑I����� |

PLL �{�[�h �ɗp�ӂ���Ă���̂� Active-network 2 �̉�H�ł��D

��

| |

| �}-17. �A�N�e�B�u�E���[�v�t�B���^�̌v�Z��� |

���̌v�Z�e�[�u���ł́CR1 �̒l�����߂�� C1 �� R2 �����܂�C�܂� R3 �̒l���� C2 �����߂邱�Ƃ��ł��܂��D

�܂��C�����̌v�Z�e�[�u���ł́CC1 �̒l���� R1 �� R2 �����܂�C�܂� C2 �̒l���� R3 �����߂邱�Ƃ��ł��܂��D

�����āC�E�̌v�Z�e�[�u���ł́CR2 �̒l���� R1 �� C1 �����߂邱�Ƃ��ł��܂��D

�����ł� �R���f���T �̒l�� �萔�����܂�I�Ԃ��Ƃ��ł��Ȃ��̂ŁCC1 �� C2 �� 0.47uF �Ƃ��܂��D

R1 �̒l�� 55.47K�� �ƎZ�o����܂����̂� 56K�� �Ƃ��CR2 �� 1.26K�� �ƎZ�o���ꂽ�̂� 1.2K�� �Ƃ��܂��D

R3 �� 90.74�� �ƎZ�o����Ă��܂��̂ŁC100���Ƃ��܂��D

�iR3�͗\���p�^�[���������C 2�̒�R�������ł���̂ŁC 82 + 18 = 100 �� �̒�R���V���[�Y�Ƃ��܂��j�D

�����āC���[�v�t�B���^�� PFC ��U�CD�o�͂�OP�A���v�̍������͂ɂȂ��ŗp��������ł��̂ŁC�}-11 �ɋL��

�萔�̐ݒ�ƂȂ�܂��D

�܂��C���̒萔�ɂ��邱�Ƃ� ���_�l���ǂꂾ�����ق����邩�� ������̃V�~�����[�V�������� �������܂��D

�Ȃ��C�{�[�h��ł̃��[�v�t�B���^�̈ʒu�́C������̎ʐ^ ���Q�Ƃ��������D

�{�[�h��ɂ́C�����Ōv�Z���� ����g�� fr = 500KHz �� �o�͎��g�� fout = 180MHz �CN = 360 �̏ꍇ�̃J�b�g�I�t

���g�� fo = 1KHz�C�ʑ��]�T ��o = 60���� ���[�v�t�B���^����������Ă��܂��D

�Ȃ��C���̒萔�ł� �Ⴆ�� ����g�� fr = 10MHz �Ƃ��āCN �����������Ă��C���b�N�͈ێ����܂����CPLL�̈���x��

�œK�ȏ�Ԃɂ���܂���D ��

���̌v�Z�c�[����p���āC���g�p�ɂȂ�����ł� ���[�v�t�B���^�̍œK���v�����Ă��������D

���@9. �Q�l�f�[�^

�ȉ��ɁC�Q�l�f�[�^�Ƃ��� �X�y�A�i�Ń��j�^���� �e�ݒ�ł� ��\�o�͔g�`�������܂��D

�\�������� �o�͔g�` �� �I�����Ă��������I

1. �o��180MHz/ 360MHz�C�X�p��50KHz�ɂ� ��

2. �o��180MHz/ 360MHz�C�X�p��5KHz�ɂ� ��

3. �o��180MHz/ 184MHz�C4MHz�X�e�b�v�C�X�p��200MHz�ɂ� ��

4. �o�� OUT1 180MHz/ OUT2 22.5MHz�C�X�p��5KHz�ɂ� ��

5. �o�� 200MHz/ ����g�� fr=200KHz�C�X�p��1MHz�ɂ� ��

6. �o�� 240MHz/ ����g�� fr=10MHz�C�X�p��50KHz�ɂ� ��

7. �o�� 200MHz/ ����g�� fr=5MHz �� fr=200KHz ��r�C�X�p��5KHz�ɂ� ��

REF�{�[�h�o�� �F

8. �o�� 10MHz VCXO�C�X�p��50MHz�ɂ� ��

9. �o�� 5MHz REF�C�X�p��50MHz�ɂ� ��

10. �o�� 1MHz REF�C�X�p��5MHz�ɂ� ��

11. �o�� 500KHz REF�C�X�p��5MHz�ɂ� ��

12. �o�� 200KHz REF�C�X�p��2MHz�ɂ� ��

URL : http://gate.ruru.ne.jp/rfdn/